### CMPT 295

Unit - Machine-Level Programming

Lecture 10 – Assembly language basics: leag instruction, memory addressing modes and arithmetic & logical operations

### Last Lecture

- As x86-64 assembly s/w dev., we now get to see more of the microprocessor (CPU) state: PC, registers, condition codes

- x86-64 assembly language Data

- 16 integer registers of 1, 2, 4 or 8 bytes + memory address of 8 bytes

- Floating point registers of 4 or 8 bytes

- No aggregate types such as arrays or structures

- x86-64 assembly language Instructions

- mov\* instruction family

- From register to register

- From memory to register

- From register to memory

- Memory addressing modes

2

Cannot do memory-memory transfer with a single mov\* instruction

## Why cannot do memory-memory transfer with a single **mov**\* instruction?

- No x86-64 assembly instructions that take 2 memory addresses as operands

- Such instruction would

- Makes for very long machine instructions

- Require more complex decoder unit (on microprocessor) in other words, require more complex microprocessor datapath

- Memory only has one data bus and one address bus

- $\Rightarrow$  No appetite for instruction set architects to create such instructions

- $\Rightarrow$  Registers very fast and can easily be used for such transfer

- More info here:

https://stackoverflow.com/questions/33794169/why-isnt-movl-frommemory-to-memory-allowed

### Last Lecture

4

Requirement: When reading/writing assembly code ...

... add a comment at the top of your function in your assembly code describing the parameter-toregister mapping swap: # xp -> %rdi, yp -> %rsi movq (%rdi), %rax # L1 = \*xp movq (%rsi), %rdx # L2 = \*yp movq %rdx, (%rdi) # \*xp = L2 movq %rax, (%rsi) # \*yp = L1 ret

Comment each of your assembly language instruction by explaining what it does using corresponding C statement or pseudocode

### Today's Menu

#### Introduction

- C program -> assembly code -> machine level code

- Assembly language basics: data, move operation

- Memory addressing modes

- Operation leag and Arithmetic & logical operations

- Conditional Statement Condition Code + cmov\*

- Loops

- Function call Stack

- Array

- Buffer Overflow

- Floating-point operations

# Various types of operands to x86-64 instructions

- 1. Integer value as operand directly in an instruction

- This operand is called immediate

- Operand syntax: Imm

- Examples: movq \$0x4, %rax and movb \$-17, %al

These instructions

copy immediate

value to register

This instruction

copies the

value of one

register into

- Registers as operands in an instruction

- Operand value: R[r<sub>a</sub>]

- Operand syntax: %r mane of particular register

- Example: movq %rax, %rdx-

- Memory address using various memory addressing modes as operands in an instruction

So far, this is the type of operands what we have seen!

### Memory addressing modes

We access memory in an x86-64 instruction by expressing a memory address through various **memory addressing modes**

1. Absolute memory addressing mode

- Use memory address as operand directly in instruction

- The operand is also called immediate

- Operand syntax: Imm

- Effect: M[Imm]

- Example: call plus

- 2. Indirect memory addressing mode

**plus** refers to the memory address of the first byte of the first instruction of the function called **plus** (see Demo)

### 2. Indirect memory addressing mode

- When a register contains an address

- Similar to a pointer in C

- To access the data at the address contained in the register, we use parentheses (...)

- General Syntax: (r<sub>b</sub>)

- Effect: M[R[r<sub>b</sub>]]

### 2. Indirect memory addressing mode

| Example:                                                | reaister to reaister<br><b>movq %rdx,%rax</b> | memorv t<br>vs <u>movq</u> (%: | o reaister<br><b>rdx) ,%rax</b> |  |

|---------------------------------------------------------|-----------------------------------------------|--------------------------------|---------------------------------|--|

| Meaning or effect:                                      | rax <- rdx                                    | VS rax <- M                    | [rdx]                           |  |

| or:                                                     | R[rax] <- R[rdx]                              | R[rax] <- M[R[rdx]]            |                                 |  |

| Befor                                                   | e After                                       | Before                         | After                           |  |

| %rax =                                                  | 15 % <b>rax = 6</b>                           | %rax = 15                      | % <u>rax</u> = 11               |  |

| %rdx =                                                  | 6 % <u>rdx</u> = 6                            | % <u>rdx</u> = 6               | % <u>rdx</u> = 6                |  |

| not used M[6] =                                         | 11  M[6] = 11                                 | M[6] = 11                      | M[6] = 11                       |  |

| Other examples: movg %rax, (%rdx) <- register to memory |                                               |                                |                                 |  |

| movg \$-147, (%rax) <- immediate to memory              |                                               |                                |                                 |  |

**Leag** has the form of an instruction that reads from memory to a register (because of the parentheses), however it \*\*\*does not\*\*\* reference **memory at all!**

C code:

10

### leaq-Load effective address instruction

- Often used for address computations and general arithmetic computations

- Syntax: leaq Source, Destination

- Example:

```

leaq (%rax, %rcx), %rdx

```

- 2. Computing arithmetic expressions of the form x + k\*y where k  $\in \{1,2,4,8\}$  if \$rdi <- variable a

- return a\*3; leaq (%rdi, %rdi, 2), %rax

- Once executed, rax will contain 3a

rdx will contain 0x18

Once executed,

- Operand Destination is a register

- Operand Source is a memory addressing mode expression

3. "**Base + displacement**" / memory addressing mode

- General Syntax: Imm(r<sub>b</sub>)

- Effect: M[Imm + R[r<sub>b</sub>]]

- Examples: movq %rax, -8(%rsp)

leaq 7(%rdi), %rax

Careful here!

11

• When dealing with leaq, the effect is  $Imm + R[r_b]$

\*\*\*  $M[Imm + R[r_b]]$

### 4. Indexed memory addressing mode

- 1. General Syntax:  $(r_b, r_i)$

- Effect:  $M[R[r_b] + R[r_i]]$

- Example: movb (%rdi, %rcx), %al

- 2. General Syntax:  $Imm(r_b, r_i)$

- Effect:  $M[Imm + R[r_b] + R[r_i]]$

- Example: movw 0xA(%rdi, %rcx), %r11w

#### **Careful here!**

- When dealing with leaq, the effect is

- **1.**  $R[r_b] + R[r_i] *** NO^{\dagger} M[R[r_b] + R[r_i]]$

- 2.  $Imm + R[r_b] + R[r_i] *** not *** M[Imm + R[r_b] + R[r_i]]$

### 5. Scaled indexed memory addressing mode

Effect:  $M[R[r_i] * s]$ 1. General Syntax:  $(, \mathbf{r}_i, \mathbf{s})$ Example: (, %rdi, 2) 2. General Syntax: *Imm(, r<sub>i</sub>, s)* Effect:  $M[Imm + R[r_i] * s]$ Example: 3(, %rcx, 8) 3. General Syntax:  $(r_{\rm b}, r_{\rm i}, s)$ Effect:  $M[R[r_b] + R[r_i] * s]$ Example: (%rdi, %rsi, 4) 4. General Syntax:  $Imm(r_b, r_i, s)$  Effect:  $M[Imm + R[r_b] + R[r_i] * s]$ Example: 8(%rdi, %rsi, 4)

#### Again, careful here!

When dealing with leag, the effect is \*\*\*not\*\*\* to reference memory at all.

### Summary - Memory addressing modes

We access memory in an x86-64 instruction by expressing a memory address through various **memory addressing modes**

- 1. Absolute

- 2. Indirect

- 3. "Base + displacement"

- 4. 2 indexed

- 5. 4 scaled indexed

General Syntax: Imm(r<sub>b</sub>, r<sub>i</sub>, s) Effect: M[Imm + R[r<sub>b</sub>]+ R[r<sub>i</sub>] \* s]

See <u>Table of x86-64 Addressing Modes</u>

on Resources web page of our course web site

### Let's try it!

| %rdx | 0xf000 |

|------|--------|

| %rcx | 0x0100 |

| Expression     | Address Computation | Address |

|----------------|---------------------|---------|

| 8(%rdx)        |                     |         |

| (%rdx,%rcx)    |                     |         |

| (%rdx,%rcx,4)  |                     |         |

| 0x80(,%rdx,2)  |                     |         |

| 0x80(%rdx, 2)  |                     |         |

| 0x80(,%rdx, 3) |                     |         |

| q<br>l<br>w | <pre>&gt; Size designator<br/>f -&gt; long 64<br/>&gt; int 32<br/>f -&gt; short 16<br/>o -&gt; char 8</pre> | Two-      | Operand Arith                                           | nmetic Instructions     | 5      |

|-------------|-------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------------------------|-------------------------|--------|

| Γ           | Synta                                                                                                       | 1X        | Meaning                                                 | Examples                | in C   |

|             | add* S                                                                                                      | Src, Dest | $\texttt{Dest} \leftarrow \texttt{Dest} + \texttt{Src}$ | c addq %rax, %rcx       | х += у |

|             | sub* S                                                                                                      | Src, Dest | $\texttt{Dest} \leftarrow \texttt{Dest} - \texttt{Src}$ | c subq %rax, %rcx       | х -= у |

|             | imul*                                                                                                       | Src, Dest | $\texttt{Dest} \leftarrow \texttt{Dest} * \texttt{Src}$ | c imulq \$16,(%rax,%rdx | x *= v |

|             |                                                                                                             |           |                                                         |                         | л — у  |

- "destination" and "first operand" are the same

- "2 operand" assembly language (machine)

- **mem**  $\leftarrow$  **mem OP mem** usually not supported

- 2 assembly code formats: ATT and Intel format (see Aside in Section 3.2 P. 177)

- We are using the ATT format

16

Both order the operands of their instructions differently - Watch out!

| q -> lo:<br>l -> in   | -> Size designator<br>A -> long 64<br>-> int 32<br>A -> short 16<br>Two-Operand Logical Instructions |         |        |                                                              |                                                  |  |

|-----------------------|------------------------------------------------------------------------------------------------------|---------|--------|--------------------------------------------------------------|--------------------------------------------------|--|

| b -> ch               |                                                                                                      | Syntax  |        | Meaning                                                      | Examples                                         |  |

|                       | and                                                                                                  | d* Src, | Dest   | $\texttt{Dest} \leftarrow \texttt{Dest}$ &                   | Src andl \$252645135, %edi                       |  |

|                       | or                                                                                                   | * Src,  | Dest   | Dest $\leftarrow$ Dest   3                                   | Src orq %rsi, %rdi                               |  |

|                       | xox                                                                                                  | r* Src, | Dest   | $\texttt{Dest} \leftarrow \texttt{Dest} \uparrow \texttt{a}$ | Src xorq %rsi, %rdi                              |  |

| xorq special purpose: |                                                                                                      |         |        |                                                              |                                                  |  |

|                       | xorq %rax, %rax <- zeroes register %rax                                                              |         |        |                                                              |                                                  |  |

|                       |                                                                                                      |         | ► movq | <b>\$0, %rax</b> <- also                                     | o zeroes register %rax                           |  |

| x86-64 convention:    |                                                                                                      |         |        |                                                              |                                                  |  |

|                       | Any instruction updating the lower 4 bytes will cause the higher-order bytes to be set to 0          |         |        |                                                              |                                                  |  |

| 17                    |                                                                                                      |         | ► xorl | <pre>%eax, %eax and mo</pre>                                 | <b>vl \$0, %eax</b> <- also zeroes register %rax |  |

### Two-Operand Shift Instructions

Meaning **Syntax Examples** salq \$4, %rax  $sal \star Src, Dest$  Dest  $\leftarrow$  Dest << Src Left shift - also called shlq: filling Dest with 0, from the right sar\* Src, Dest □ Dest ← Dest >> Src sarl %cl, %rax Right arithmetic Shift: filling Dest with sign bit, from the left shr\* Src, Dest □ Dest ← Dest >> Src shrq \$2, %r8

Right logical Shift: filling Dest with 0, from the left

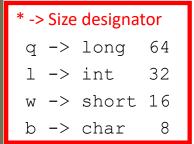

| * -> Size designator |    |       |    |  |

|----------------------|----|-------|----|--|

| q                    | -> | long  | 64 |  |

| l                    | -> | int   | 32 |  |

| W                    | -> | short | 16 |  |

| b                    | -> | char  | 8  |  |

### One-Operand Arithmetic Instructions

| Syntax           | Meaning                                               | Examples    |

|------------------|-------------------------------------------------------|-------------|

| inc* <i>Dest</i> | $\texttt{Dest} \leftarrow \texttt{Dest} + \texttt{1}$ | incq (%rsp) |

| dec* <i>Dest</i> | $\texttt{Dest} \leftarrow \texttt{Dest} - \texttt{1}$ | decq %rsi   |

| neg* <i>Dest</i> | $\texttt{Dest} \leftarrow -\texttt{Dest}$             | negl %eax   |

| not* <i>Dest</i> | $\texttt{Dest} \leftarrow \texttt{~Dest}$             | notq %rdi   |

### Summary

- leag load effective address instruction

- Various types of operands to x86-64 instructions

- Immediate (constant integral value)

- Register (16 registers)

- Memory address (various memory addressing modes)

- •General Syntax:  $Imm(r_b, r_i, s)$

- Arithmetic & logical operations

- Arithmetic instructions: add\*, sub\*, imul\* inc\*, dec\*, neg\*, not\*

- Logical instructions: and\*, or\*, xor\*

- Shift instructions: sal\*, sar\*, shr\*

### Next lecture

#### Introduction

- C program -> assembly code -> machine level code

- Assembly language basics: data, move operation

- Memory addressing modes

- Operation leag and Arithmetic & logical operations

Practice and DEMO!

- Conditional Statement Condition Code + cmov\*

- Loops

- Function call Stack

- Array

- Buffer Overflow

- Floating-point operations